半导体芯片ESD敏感度测试

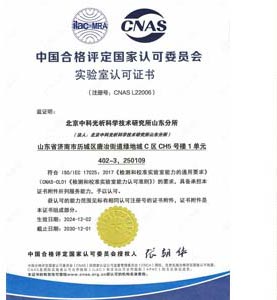

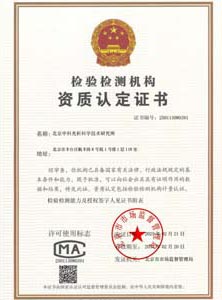

承诺:我们的检测流程严格遵循国际标准和规范,确保结果的准确性和可靠性。我们的实验室设施精密完备,配备了最新的仪器设备和领先的分析测试方法。无论是样品采集、样品处理还是数据分析,我们都严格把控每个环节,以确保客户获得真实可信的检测结果。

信息概要

半导体芯片ESD敏感度测试是评估芯片在静电放电环境下的抗干扰能力和可靠性的重要检测项目。静电放电(ESD)是半导体器件在制造、运输和使用过程中常见的潜在威胁,可能导致芯片性能下降或永久性损坏。通过的ESD敏感度测试,可以确保芯片符合行业标准(如JEDEC、AEC-Q100等),提高产品可靠性和市场竞争力。

检测的重要性在于:ESD事件可能直接导致芯片功能异常或失效,尤其在汽车电子、医疗设备等高可靠性领域,ESD防护能力直接影响终端产品的安全性和寿命。第三方检测机构通过标准化测试流程,为客户提供客观、准确的ESD性能评估报告。

检测项目

- 人体模型(HBM)ESD测试

- 机器模型(MM)ESD测试

- 充电器件模型(CDM)ESD测试

- 传输线脉冲(TLP)测试

- 非常快速传输线脉冲(VF-TLP)测试

- ESD敏感度分级测试

- ESD防护器件性能测试

- ESD失效阈值电压测试

- ESD失效电流测试

- ESD失效能量测试

- ESD失效模式分析

- ESD防护电路响应时间测试

- ESD事件后功能恢复测试

- ESD多次冲击耐受性测试

- ESD热插拔敏感性测试

- ESD耦合干扰测试

- ESD辐射敏感度测试

- ESD传导敏感度测试

- ESD防护器件钳位电压测试

- ESD防护器件漏电流测试

检测范围

- 逻辑芯片

- 存储器芯片

- 微处理器

- 模拟芯片

- 混合信号芯片

- 射频芯片

- 功率半导体器件

- 传感器芯片

- 图像传感器

- 显示驱动芯片

- 电源管理芯片

- 通信芯片

- 汽车电子芯片

- 工业控制芯片

- 消费电子芯片

- 医疗电子芯片

- 航空航天芯片

- FPGA芯片

- ASIC芯片

- SoC芯片

检测方法

- 人体模型(HBM)测试方法:模拟人体带电接触芯片时的放电过程

- 机器模型(MM)测试方法:模拟金属设备带电接触芯片时的放电过程

- 充电器件模型(CDM)测试方法:评估芯片自身带电后放电的敏感性

- 传输线脉冲(TLP)测试:通过可控短脉冲分析器件ESD特性

- 非常快速传输线脉冲(VF-TLP)测试:用于纳秒级快速ESD事件分析

- IEC 61000-4-2标准测试:评估系统级ESD抗扰度

- JEDEC JESD22-A114标准测试:规范HBM ESD测试流程

- JEDEC JESD22-A115标准测试:规范MM ESD测试流程

- JEDEC JESD22-C101标准测试:规范CDM ESD测试流程

- AEC-Q100-002标准测试:汽车电子HBM ESD测试要求

- AEC-Q100-003标准测试:汽车电子MM ESD测试要求

- 失效分析显微镜检查:观察ESD损伤的物理特征

- 电参数测试对比法:比较ESD前后器件电参数变化

- 功能测试验证法:验证ESD事件后芯片功能完整性

- 热成像分析法:通过热分布评估ESD失效点

检测仪器

- ESD模拟器

- 传输线脉冲(TLP)测试系统

- 非常快速传输线脉冲(VF-TLP)测试系统

- 静电放电测试台

- 高压脉冲发生器

- 示波器

- 电流探头

- 电压探头

- 参数分析仪

- 半导体特性分析系统

- 失效分析显微镜

- 热成像仪

- 静电电压表

- 接地电阻测试仪

- 电磁屏蔽测试箱

注意:因业务调整,暂不接受个人委托测试。

以上是关于半导体芯片ESD敏感度测试的相关介绍,如有其他疑问可以咨询在线工程师为您服务。

了解中析

实验室仪器

合作客户